# A Comparative Study of CMOS Transimpedance Amplifier (TIA)

Priya Singh, Vandana Niranjan, Ashwni Kumar

Abstract: In this paper a comparative study of different CMOS transimpedance amplifier has been presented. Standard device parameters of transimpedance amplifier such as gain, input refereed noise, power dissipation and group delay are studied and compared. Here the transimpedance amplifier is divided on the basis of its topology and device technology used and performance is summarized to get the overview. Most of the analysis taken are performed on 0.18 µm technology and some are implemented using 45nm, 0.13µm, 65nm, and 90nm.

Keywords: CMOS, Transimpedance, Amplifier (TIA), Technology

#### **INTRODUCTION** I.

In today's intelligence technology various sensors are used to convey the information signal. Most of the sensors convert this information containing signal to current signal but these signals cannot be further processed since most of the subsequent blocks in a system work in voltage mode. Therefore, it is mandatory to convert this current signal to amplified voltage signal. This conversion can be carried out using transimpedance amplifier (TIA). Transimpedance amplifier can be designed using active and passive circuit elements. Passive circuit elements have many limitations in VLSI designing such as larger chip area, higher power dissipation and so on thus active elements are used more often such as BJT, MOSFET or an operational amplifier. While designing a Practical Transimpedance Amplifier Main Characteristics of concern are low input impedance, low output impedance, high transimpedance gain, high bandwidth and low noise. In this paper main concern is on CMOS transimpedance amplifier. Further section II presents different topologies of CMOS transimpedance amplifier and section III includes comparative study analysis of CMOS existing transimpedance amplifier on the basis of topology and device technology used.

Manuscript received on 12 January 2023 | Revised Manuscript received on 25 February 2023 | Manuscript Accepted on 15 March 2023 | Manuscript published on 30 March 2023.

| * Correspondence Author                                                   |  |  |  |  |

|---------------------------------------------------------------------------|--|--|--|--|

| Priya Singh*, Research Scholar, Indira Gandhi Delhi Technical             |  |  |  |  |

| University for Women, Kashmeri Gate, Delhi, India. E-mail:                |  |  |  |  |

| priya004phd17@igdtuw.ac.in, ORCID ID: https://orcid.org/0000-0003-        |  |  |  |  |

| <u>0716-764X</u>                                                          |  |  |  |  |

| Dr. Vandana Niranjan, Professor, Indira Gandhi Delhi Technical            |  |  |  |  |

| University for Women, Kashmeri Gate, Delhi, India. E-mail:                |  |  |  |  |

| vandana_niranjan@yahoo.com                                                |  |  |  |  |

| Prof. Ashwni Kumar, Professor, Indira Gandhi Delhi Technical              |  |  |  |  |

| University for Women, Kashmeri Gate, Delhi, India. E-mail:                |  |  |  |  |

| drashwnikumar@gmail.com                                                   |  |  |  |  |

|                                                                           |  |  |  |  |

| © The Authors. Published by Lattice Science Publication (LSP). This is an |  |  |  |  |

| open access article under the CC-BY-NC-ND license                         |  |  |  |  |

| (http://creativecommons.org/licenses/by-nc-nd/4.0/)                       |  |  |  |  |

|                                                                           |  |  |  |  |

Retrieval Number: 100.1/iivlsid.A1215033123 DOI:10.54105/ijvlsid.A1215.033123 Journal Website: www.ijvlsi.latticescipub.com

# **II. TOPOLOGIES OF CMOS TRANSIMPEDANCE AMPLIFIER**

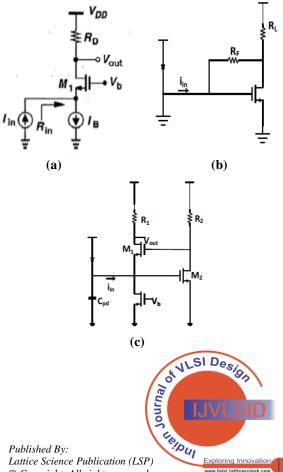

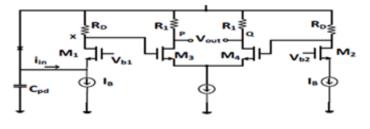

A number of research papers published related to CMOS transimpedance amplifier were studied. [1-40] Based on the literature review most of the reported CMOS transimpedance amplifier can be broadly classified in to four types- common gate topology, common source topology, regulated cascode topology and differential topology. Most of the transimpedance amplifier used these basic topologies or hybridized form are used for further improvement. In common gate topology input impedance is low as compared to other topology due to proper bias current. Due to this high bandwidth can be achieved. Noise is the major issue of common gate topology when used in low supply voltage. Common source topology have high driving capability but as the device size minimize transistors breakdown voltage also reduces. Due to this tradeoff amid transimpedance gain and voltage headroom is very crucial for common source topology. Effect of parasitic capacitance on bandwidth can be reduced by cascode structure in regulated cascode topology but due to severe trade off in all characteristics more improvement in circuit is required. Differential structure results in less offset noise and cannot be used alone due to deferential input a converter is always needed that makes circuit more complex.

© Copyright: All rights reserved.

# A Comparative Study of CMOS Transimpedance Amplifier (TIA)

(**d**)

Figure 1. (a) Common gate TIA topology [36] (b) Common source TIA topology [13] (c) Regulated Cascode TIA topology [33] (d) Differential TIA topology [36]

## III. COMPARATIVE STUDY OF CMOS TIA

Comparison of some of the transimpedance amplifier designed with best characteristic achieved so far is refereed in table 1 in ascending order of publication year. Best result obtained among them for each characteristics are highlighted. In table 2 the latest transimpedance amplifier based on device technology used are compared. CMOS technology was always in lime light due to its low cost, low power dissipation and integrity property, but due to its parasitic properties and degraded noise performance design of TIA becomes challenging. Various research gaps had been identified based on this study. Common gate topology of CMOS TIA cannot work at low supply voltage efficiently because of degraded noise performance. Nano scale application cannot use common source TIA due to less voltage headroom thus high bit error rate. Regulated cascode topology provides best isolation from parasitic capacitance but severe tradeoff between gain and bandwidth reduces the efficiency.

| Ref.<br>No. | Year | Topology /technique                                   | Power supply<br>(volts) | Gain<br>D Bohms | BW           | Input Referred<br>Noise (pA/√Hz) | Power<br>dissipation<br>M W |

|-------------|------|-------------------------------------------------------|-------------------------|-----------------|--------------|----------------------------------|-----------------------------|

| [8]         | 1991 | GaAs FET                                              | -                       | -               | 100 MHz      | -                                | -                           |

| [12]        | 1999 | C peaking technique                                   | -                       | 0.95            | 2.3 GHz      | -                                | -                           |

| [14]        | 2002 | hybrid topology                                       | -                       | 20              | 1 Ghz        | -                                | 27                          |

| [9]         | 2004 | Regulated cascade                                     | 5                       | 58              | 950 MHz      | 6.3                              | 85                          |

| [21]        | 2004 | Interstage matching<br>network technique              | 2.5                     | 54              | 9.2 GHz      | -                                | -                           |

| [10]        | 2006 | Regulated cascade                                     | 2                       | 52              | 7.6GHz       |                                  | 34                          |

| [27]        | 2007 | Regulated cascade                                     | 1.8                     | 53              | 8GHz         | 18                               | 13.5                        |

| [5]         | 2007 | Common base-<br>BiCMOS                                |                         | 65.2            | 7.2GHz       | 17.7                             | 56.6                        |

| [29]        | 2010 | Common gate with<br>active feedback                   | 1.8                     | 54.6            | 7GHz         | 17.5                             | 18.6                        |

| [32]        | 2012 | Regulated Cascode                                     |                         | 52              | <u>35GHz</u> | 14                               | -                           |

| [34]        | 2012 | SOI technology                                        | -                       | 55              | 33GHz        | 20.47                            | -                           |

| [39]        | 2014 | Common gate                                           | -                       | <u>104.2</u>    | 19MHz        | -                                | -                           |

| [19]        | 2015 | Differential                                          |                         | 87.8            | 1.4GHz       | -                                | 8.1                         |

| [3]         | 2015 | Regulated Cascode                                     | 3.3                     | 61              | 15GHz        | -                                | 32                          |

| [24]        | 2015 | Regulated cascade                                     | -                       | -               | 9GHZ         | -                                | -                           |

| [18]        | 2015 | Regulated cascade                                     | 1.5                     | 50              | 7GHz         | 31                               | -                           |

| [17]        | 2016 | Differential with<br>Regulated Cascode<br>input stage | 1.8                     | 18              | 870 MHz      | <u>6</u>                         | 27                          |

| [15]        | 2017 | Common gate using<br>FGMOS                            | <u>1</u>                | 37.7            | 13.5GHz      | -                                | <u>1.1</u>                  |

| [40]        | 2018 | BiCMOS tech.                                          | -                       | 67              | 28GHz        | 10                               | 95                          |

Table 1. Comparison of Various TIA Designed

Table 2. Performance Comparison of Latest Existing TIA Using Different Device Technology

| Technology<br>And devices | Paper no.                                                 | Bandwidth (GHz) | Input referred<br>noise (pA/√Hz) | $\begin{array}{c} Gain\left(Z_{T}\right) \\ dB\Omega \end{array}$ | Power Dissipation<br>mw |

|---------------------------|-----------------------------------------------------------|-----------------|----------------------------------|-------------------------------------------------------------------|-------------------------|

| Bi CMOS 130 nm            | IEICE<br>transaction<br>2018[40]                          | 28              | <u>10</u>                        | <u>67</u>                                                         | 95                      |

| FGMOS 0.18µm              | Integration: the<br>VLSI journal:<br>ELSEVIER<br>2018[15] | 13.5            | -                                | 37.7                                                              | <u>1.1</u>              |

| CMOS 65nm                 | ISCAS 2012[35]                                            | <u>35</u>       | 14                               | 52                                                                | 168                     |

| SOI CMOS 45nm             | JSSC 2012[34]                                             | 33              | 20.47                            | 55                                                                | 9                       |

#### IV. CONCLUSION

Apart from topology device technology is playing major issue in improving the characteristics especially when low voltage and low power is concerned. FGMOS as active feedback provides best result in terms of low power supply and power dissipation. BiCMOS gives most consistent result in terms of all characteristics. All topologies are improvised and further improvement can be done to attain the best characteristics by introducing several techniques of bandwidth enhancement and hybridizing these topologies to take the advantage of each. These improved TIA can enhance the performance of intelligent system and application in receiving and transmission of various information carrying signal.

# **FUTURE WORK**

Design of transimpedance amplifier necessitates efficient tradeoff and improvisation of each characteristic. Low voltage circuit techniques such as FGMOS, QFGMOS, bulk driven, DTMOS etc can be used for low voltage application and reducing the power consumption. Various noise reduction techniques could be used in the TIA circuit to optimize the noise performance. Further cascading of different stages will improve the gain as well as improve the parasitic capacitance effect to improve the bandwidth requirement.

### DECLARATION

| Funding/ Grants/<br>Financial Support                     | No, I did not receive.                                              |

|-----------------------------------------------------------|---------------------------------------------------------------------|

| Conflicts of Interest/<br>Competing Interests             | No conflicts of interest to the best of our knowledge.              |

| Ethical Approval and<br>Consent to                        | No, the article does not require<br>ethical approval and consent to |

| Participate<br>Availability of Data<br>and Material/ Data | participate with evidence.<br>Not relevant.                         |

| Access Statement                                          |                                                                     |

| Authors<br>Contributions                                  | All authors have contributed equally.                               |

## REFERENCE

- 1. X Huang, Cha, D Zhao, B Guo, M Je, H Yu "Transimpedance Amplifier for Integrated 3D Ultrasound Biomicroscope Applications", , World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering, Vol:6, No:9, 2012

- 2. Praveen Dwivedi, Amit Kumar Singh and R.G. Sangeetha "A Comparative Analysis of Transimpedance Amplifier in Giga-bit Optical Communication "Research Journal of Engineering Sciences ISSN 2278 - 9472 Vol. 3(3), 6-9, March (2014)

- Q Song, LMao "Wideband sige BICMOS transimpedance amplifier 3. foe 20 Gb/s optical links", IEICE electronics express, Vol. 12, No. 13, july 2015, 1-8 [CrossRef]

- T. Ridder, P. Ossieur, X. Yin, B. Baekelandt, C. Me'lange, J. 4. Bauwelinck, X.Z. Qiu and J. Vandewege, "Bicmos variable gain transimpedance amplifier for automotive applications" The Institution of Engineering and Technology 2008 28 October 2007 Electronics Letters online no: 20083101 [CrossRef]

- 5. F. Touati and M. Loulou, "High-Performance bicmos Transimpedanc Amplifiers for Fiber-Optic Receivers", The Journal of Engineering Research Vol. 4, No.1 (2007) 69-74 [CrossRef]

- Douglas Bespalko ,"Transimpedance Amplifier Design using 0.18 6. µm CMOS Technology" ,thesis Queen's University Kingston, Ontario, canadajuly 2007

Retrieval Number: 100.1/ijvlsid.A1215033123 DOI:10.54105/ijvlsid.A1215.033123 Journal Website: www.ijvlsi.latticescipub.com 7. Taghavi, , Belostotski, James W. Haslett, Ahmadi , "10-Gb/s 0.13um CMOS Inductorless Modified-RGC Transimpedance Amplifier" IEEE Transactions On Circuits And Systems-I: Regular Papers, Vol. 62, No. 8, August 2015 [CrossRef]

- 8. N Scheinberg, , R.J. Bayruns, and T.M. Laverick , "Monolithic GaAs Transimpedance Amplifiers for Fiber-optic Receivers", IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 26, NO. 12, DECEMBER 1991 [CrossRef]

- 9. "1.25-Gb/s M.Park. and H.J Y00, Regulated . cascodecmostransimpedance Amplifier for Gigabit Ethernet Applications ", IEEE Journal Of Solid-State Circuits, Vol. 39, No. 1, January 2004 [CrossRef]

- H.Y.Hwang, J.C. Chien , "A CMOS Tunable Transimpedance 10. Amplifier<sup>w</sup>, *IEEE Microwave And Wireless Components Letters*, Vol. 16, No. 12, December 2006 [CrossRef]

- S Goswami, J Silver, T Copani, W Chen, Hugh J. Barnaby, Bert 11. Vermeire, Sayfe Kiaei , "A 14mw 5Gb/s CMOS TIA with Gain-Reuse Regulated Cascode Compensation for Parallel Optical Interconnects", IEEE International Solid-State Circuits Conference, 2009 [CrossRef]

- 12. F.T. Chien and Y.C.Chan, "Bandwidth Enhancement of Transimpedance Amplifier by a Capacitive-Peaking Design ", IEEE Journal Of Solid-State Circuits, Vol. 34, No. 8, August 1999 [CrossRef]

- M. Ahmed, "Transimpedance Amplifier (TIA) Design for 400 Gb/s Optical Fiber Communications". *thesis for M.S. Virginia Polytechnic* 13 Institute and State University, May 02, 2013 Blacksburg, VA

- 14. J Lee, S.J. Song, S. Park, C. Nam1, Y. Kwon and H. Yoo, Multichip on Oxide of 1Gb/s 80db Fully- Differential CMOS Transimpedance Amplifier for Optical Interconnect Applications", ISSCC 2002 / SESSION 4 / BACKPLANE INTERCONNECTED Ics /4.7

- U. Bansal, M. Gupta , "High bandwidth transimpedance amplifier 15 using FGMOS for low voltage operation", INTEGRATION, the VLSI journal, ELSEVEIR, 2017 [CrossRef]

- Claudio Talarico  $\cdot$  G. Agrawal  $\cdot J.$  -Roveda  $\cdot$  H. ,Design "Optimization 16 of a Transimpedance Amplifier for a Fiber Optic" Springer Science+Business Media New York 2015 [CrossRef]

- 17. G. Royo, C. Sánchez-Azqueta, C. Aldea, and S. Celma , "CMOS Transimpedance Amplifier with Controllable Gain for RF Overlay", 2016 IEEE journal. [CrossRef]

- 18. M. Seifouri n, parvizamiri, majidrakide ,"Design of broadband transimpedance amplifier for optical communication systems", 2015 ELSEVIER- optik LTD [CrossRef]

- 19. Liu, Jiao Zo, N. Maa, Z. Zhu, Y. Yang , "A CMOS transimpedance amplifier with high gain and wide dynamicrange for optical fiber sensing system ", Optik 126 (2015) 1389-1393 , ELSEVIER [CrossRef]

- Z. Lu, K. Seng Yeo, J. Ma, , M. Do, , Wei Meng Lim, Xueying Chen 20. "Broad-Band Design Techniques for transimpedance amplifier", IEEE Transactions On Circuits And Systems: Regular Papers, Vol. 54, No. 3, March 2007 [CrossRef]

- Hajimiri, "Bandwidth Enhancement for B. Analui, and A. 21. Transimpedance Amplifiers", IEEE Journal Of Solid-State Circuits, Vol. 39, No. 8, August 2004 [CrossRef]

- 22. Z Lu, Kiat S Yeo, W Lim, M Do "Gm-boosted differential transimpedance amplifier architecture" IEICE Electronics Express · August 2007

- 23. Z Lu, K Seng Yeo, W Lim, M Do "Design of a CMOS broadband transimpedance Amplifier With Active Feedback", IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 18, No. 3, March 2010 [CrossRef]

- T.-C. Chen, C Chan, and RSheen "Transimpedance Limit Exploration 24. and Inductor-Less Bandwidth Extension for Designing Wideband Amplifiers" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Syst. 24.1 (2016) 348-352. [CrossRef]

- B. Analui and A. Hajimiri, "Bandwidth Enhancement for 25. Transimpedance Amplifiers", IEEE Journal of Solid-State Circuits, vol. 39, no. 8, pp. 1263-1270, August 2004. [CrossRef]

- C.T. Chan and O. T. C. Chen, "Inductor-less 10Gb/s CMOS 26. Using Source-follower Regulated Transimpedance Amplifier Cascode and Double Three-order Active Feedback", International Symposium on Circuits and Systems (ISCAS), pp.-5487-5490, May 2006

Published By: Lattice Science Publication (LSP)

21

© Copyright: All rights reserved.

- Z. Lu, K. S. Yeo and J. Ma, "Broad-Band Design Techniques for Transimpedance Amplifiers", *IEEE Transactions on Circuits and Systems—I: Regular Papers*, vol. 54, no. 3, pp.- 590– 600, March 2007. [CrossRef]

- T. H. Ngo, T. W. Lee and H. H. Park, "Design of Transimpedance Amplifier for Optical Receivers in 0.13 μm CMOS", *International Conference on Optical Internet (COIN)*, pp.-1-3, July 2010.

- Z. Lu, K. S. Yeo, W. M. Lim and M. A. Do, "Design of a CMOS Broadband Transimpedance Amplifier With Active Feedback", *IEEE Transactions on VLSI Systems*, vol. 18, no. 3, pp.- 1964 – 1972, March 2010. [CrossRef]

- J. D. Jin and Shawn S. H. Hsu , "A 40-Gb/s Transimpedance Amplifier in 0.18-µm CMOS Technology", *IEEE Journal of Solid-State Circuits*, vol. 43, no. 6, pp. 520-5123, June 2008. [CrossRef]

- C. F. Liao and S. L. Liu, "40 Gb/s Transimpedance-AGC Amplifier and CDR Circuit for Broadband Data Receivers in 90 nm CMOS", *IEEE Journal of Solid-State Circuits*, vol. 43, no. 3, pp. 642 - 655 March 2008. [CrossRef]

- J. Kim and J. F. Buckwalter, "Bandwidth Enhancement with Low Group-Delay Variation for a 40-Gb/s Transimpedance Amplifier", *IEEE Transactions on Circuits and Systems—I: Regular Papers*, vol. 57, no. 8, pp.-1964 – 1972, August 2010. [CrossRef]

- S. Bashiri, C. Plett, J. Aguirre and P. Schvan "A 40 Gb/s Transimpedance Amplifier in 65 nm CMOS", *International Symposium on Circuits and Systems (ISCAS)*, pp- 757-760, May 2010. [CrossRef]

- J. Kim and J. F. Buckwalter "A 40-Gb/s Optical Transceiver Front-End in 45 nm SOI CMOS", *IEEE Journal of Solid-State Circuits*, vol. 47, no. 3, pp. 1-4, March 2012. [CrossRef]

- S. T. Chou, S. H. Huang, Z. H. Hong, and W. Z. Chen "A 40 Gbps Optical Receiver Analog Front-End in 65 nm CMOS", *International* Symposium on Circuits and Systems (ISCAS), pp.-1736-1739, May 2012.

- 36. Behzad Razavi-"Design of Integrated Circuits for Optical Communications".

- S. H. Huang, W.Z. Chen, Y.W. Chang, and Y.T. Huang, "A 10-Gbps CMOS Single Chip Optical Receiver with 2-D Meshed Spatially-Modulated Light Detector," IEEE J. Solid-State Circuits , pp. 1158-1169, vol. 46, NO. 5, May, 2011. [CrossRef]

M jalai, Mohammed k. , "Gm boosted differential transimpedance

- M jalai, Mohammed k., "Gm boosted differential transimpedance amplifier architecture", *Electronics Express, IEICE, 2007* [CrossRef]

- A Chaddad, C Tanougast, "low- noise amplifier dedicated to biomedical devices", *IEEE conference*, 2014

- X LUO, Y Chang, "A44Gbit/sec wide dynamic range and high linearity transimpedance amplifier 130nm bicmos technology", *IEICE TRANSACTIONS on Fundamentals of Electronics Communications and Computer Sciences* Vol.E101-A No.2 pp.438-440, feb 2018 [CrossRef]

## **AUTHORS PROFILE**

**Priya Singh** had done B.E from Gyan Ganga College of Technology Jabalpur in electronics and communication and M.tech from Banasthali University Jaipur, in VLSI Design. She have teaching experience in Rajasthan Technical University and Abdul Kalam Technical University formerly known as UPTU. She had served as registered evaluator of the U.P state technical university for two years and had worked with

Bhabha Atomic Research Centre, Mumbai as project intern in microelectronics domain for one year. She had given many publications in the field of hardware implementation of adhoc protocol in international conference and journals. She had worked in the field of ASIC designing and channel implementation using FPGA and published few research in international journals. Presently she is perusing Phd in analog IC designing from Indira Gandhi Delhi technical university for women, Delhi.

**Dr. Vandana Niranjan** is working as an Professor in Department of Electronics and Communication Engineering at Indira Gandhi Delhi Technical University Delhi. She received her B.E. degree in Electronics and Communication Engineering in the year 2000 from Government Engineering College (now University Institute of Technology of Rajiv Gandhi

Proudyogiki Vishwavidyalaya) Bhopal. She received her M. Tech degree in the year 2002 from the Department of Electronics and Communication Engineering at Indian Institute of Technology Roorkee with VLSI Design as specialization. She pursued her research interest and was awarded her Ph.D degree in the area of Low Voltage VLSI Design from University School of Engineering & Technology, GGSIP University Delhi in the year 2015. She

Retrieval Number:100.1/ijvlsid.A1215033123 DOI:<u>10.54105/ijvlsid.A1215.033123</u> Journal Website: <u>www.ijvlsi.latticescipub.com</u> has a teaching and research experience of approximately 15 years at Indira Gandhi Delhi Technical University Delhi. She is member of I.E.T.E India, Institution of Engineers India and IEEE & Women in Engineering USA. She has published over 15 papers in reputed International Journals. She has also published over 35 papers in IEEE International/national conferences. (https://www.researchgate.net/profile/Dr\_Vandana\_Niranjan/publications)

**Prof. Ashwni Kumar** did his Ph.D (ECE) from Delhi University, M.E. (ECE) from Delhi College of Engineering, B.E. (ECE) from Delhi College of Engineering and MBA from FMS, Delhi University. He is at IGDTUW from the last two years. He has 16 Years of Research and Development experience in C-DOT, Research & development Center of Ministry of

communication, Govt. of India.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of the Lattice Science Publication (LSP)/ journal and/ or the editor(s). The Lattice Science Publication (LSP)/ journal and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Published By: Lattice Science Publication (LSP) © Copyright: All rights reserved.