# A Comparative Analysis of Gain and Bandwidth of **CMOS** Transimpedance Amplifier

# Vineeta Singh, Sarika Parihar, Vandana Niranjan

Abstract: The paper presents the various trans-impedance amplifier (TIA) topologies has been studied and presented with an insight of their Gain and Bandwidth. The device parameters such as gain and bandwidth has been studied and compared for various TIA topologies. The performance of the presented topologies of TIA has been compared and summarized to get an overview. The comparison is done on the basis of its topology and device technology along with gain, bandwidth and power supply. In this paper recent advancement and future scope are also discussed.

Keywords: Trans-Impedance Amplifier (Tia), Topology, High Gain, Bandwidth.

# I. INTRODUCTION

In recent years where many type of signals are used to convey the information such as optical signal in optical communication system, thermal rays etc. which compel us to study optical communications system. This TIA has many applications other than the optical fiber communication such as in automobile, Radio frequency and instruments used in medical etc. At receiver side this TIA is placed first which plays a major role for entire receiver system in terms of performance [20], consist of a photodiode for converting the light signal into a current carrying electrical signal which is amplified further converted into voltage signal. Transimpedance amplifier are needed to provide large bandwidth, high gain along with low power consumption[19]. There are some issue in TIA as well such as Noise which is of main concern that should be taken care off while designing[32]. A transimpedance amplifier is basically a current-to-voltage converter and the ratio between its input current and its output voltage is called transimpedance, Ztr is often characterized as transimpedance gain, given by following equation:

$$Z_{tr} = \frac{V_{out}}{I_{in}} \tag{1}$$

The paper is organized as follow: Section I. gives a basic idea about transimpedance amplifier (TIA) and its importance. Further, section II. In this various CMOS transimpedance amplifier (TIA) topologies are presented, in section III provides a discussion on the recent advancement.

Manuscript received on 24 January 2022 | Revised Manuscript received on 06 February 2022 | Manuscript Accepted on 15 March 2022 | Manuscript published on 30 March 2022. Correspondence Author

Vineeta Singh\*, Dept of Electronics & Communication Engineering, Indira Gandhi Delhi Technical University, for Women New Delhi, India. Email. Vineeta1009@gmail.com

Sarika Parihar, Dept of Electronics & Communication Engineering, Indira Gandhi Delhi Technical University, for Women New Delhi, India

Vandana Niranjan, Dept of Electronics & Communication Engineering, Indira Gandhi Delhi Technical University, for Women New Delhi, India

© The Authors. Published by Lattice Science Publication (LSP). This is open access article under the CC-BY-NC-ND license an (http://creativecommons.org/licenses/by-nc-nd/4.0/)

Retrieval Number: 100.1/ijvlsid. C1206031322 DOI:10.54105/ijvlsid.C1206.031322 Journal Website: www.ijvlsi.latticescipub.com

Section IV includes future scope and comparative study of parameters like gain and bandwidth along with topology and technology node used for various transimpedance amplifier.

#### II. **TIA TOPOLOGIES**

For achieving various parameters such as Gain, Bandwidth etc. numerous configuration of TIA design has been shown.

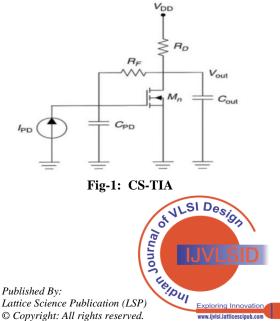

#### A. **Common source**

In short (CS-TIA) topology a shunt-shunt feedback is used to reduce the input and output impedance. This CS-TIA is shown in figure.1 [26].In CS-TIA Topology, R<sub>F</sub> is shunt feedback resistance, is used to give low input impedance. Resistive load (R<sub>D</sub>), provides wideband response. Due to reduced input impedance this configuration will increase the bandwidth and provide high open loop gain [37] and reduced output impedance provides better driving capability. The sensitivity of common source TIA mainly depends on input node capacitance (CPD), feedback resistor (RF) and trans-conductance of input transistor. Trade-off between the gain and voltage is much more crucial for common source TIA because of Miller effect. This is one of the simplest configuration which is popularly used. Open loop Gain (Acs) and BW of a common-source TIA are shown as: -

$$A_{CS} = -g_m R_0 \tag{2}$$

Where, gm is the trans-conductance of  $M_n$  and  $R_O$  is the OL output resistance which is shown as:

$$Ro = \frac{R_D R_{DS}}{R_D + R_{DS}}$$

(3)

Here, R<sub>D</sub> is drain resistance shown in figure.1. and R<sub>DS</sub> drain to source resistance Mn. Bandwidth (BW) of a common source TIA is

$$BW = \frac{A+1}{2\pi(R_O + R_F)C_{in}} \tag{4}$$

C<sub>in</sub> is the capacitance at input, addition of C<sub>PD</sub> and Miller capacitance.

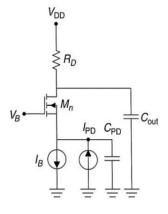

## B. Common gate

In short (CG-TIA) topology is also one of the simplest Trans-impedance amplifier topology presented in figure.2 [26] CG-TIA offers the low input impedance which in turn increases the bandwidth (BW) of the circuit along with low power consumption [30]. But at low supply voltages, noise is one of the main concern in common gate TIA topology. Its open loop Gain( $A_{CG}$ ) and Bandwidth (BW) are given below:

## Fig-2: CG-TIA

Open loop gain (A<sub>CG</sub>) of Common Gate topology as- $A_{CG} = -g_m R_0$  (5)

Here,  $g_m$  is the transconductance of  $M_n$  and  $R_{out}$  is the output resistance.

Bandwidth of Common Gate TIA is  $BW = \frac{g_m}{2\pi c_{pd}}$ (6)

Here, C<sub>pd</sub> is photodiode capacitance.

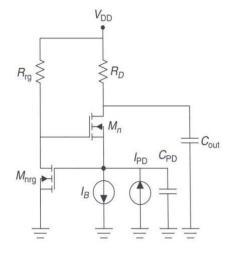

### C. Regulated cascode TIA (RGC-TIA)

Topology which was earlier also known as common-gate TIA (CG-TIA) presented in figure. 3 [26]. This configuration offers less input impedance which provides high BW and less power consumption. Using the cascade structure in RGC topology, parasitic capacitance effect on bandwidth can be reduced. Here common source configuration MOSFET work as feedback for common gate configuration MOSFET, due to this the effective transconductance of whole circuit in increased thus the pole due to parasitic capacitance is isolated this leads to improved bandwidth.

The typical Regulated cascade amplifier suffers from the trade-off between the gain, bandwidth (BW) and input referred noise  $(I_N)$ .

Voltage gain

$$(A_{RG})$$

of  $M_{nrg}$  shown as

$$A_{RG} = -g_{mnrg} \frac{R_{DS}R_{rg}}{R_{DS}+R_{rg}}$$

(7)

Where  $g_{mnrg}$  is the transconductance of  $M_{nrg}$  and  $R_{rg}$  is the resistance of  $M_{nrg}$  (regulating amplifier)

And, BW of Regulated cascade Transimpedance amplifier is-

$$BW = \frac{g_{mn}}{2\pi c_{pd}} \tag{8}$$

Fig-3: Regulated cascade TIA (RGC-TIA)

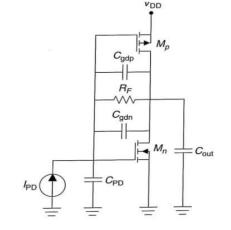

# D. Inverter TIA (Inv-TIA)

This topology is having a edge in terms of higher gain  $A_{inv}$  compared to CS-TIA shown in figure.4 [26] This circuit offers high transconductance gain  $(g_{mn}+g_{mp} \approx 2 g_m)$  which gives large Gain-Bandwidth (GBW) product as well as high OL gain  $(A_{Inv})$  with less power consumption. But, compared to CS-TIA this Inv-TIA is better.

OL Gain  $(A_{inv})$  of Inverter Transimpedance amplifier shown as-

$$A_{inv} = -g_m R_0 = -(g_{mn} + g_{mp}) R_0 \tag{9}$$

Here  $g_{mn}$  and  $g_{mp}$  are transconductances of nmos (M<sub>n</sub>) and pmos (M<sub>p</sub>) respectively and  $R_o$  is the open-loop resistance ( $R_o$ ). Where R<sub>o</sub> is

$$R_o = \frac{R_{DSN} * R_{DSP}}{1 + R_{DSN} * R_{DSP}} \tag{10}$$

Here,  $R_{DSN}$  and  $R_{DSP}$  are the drain to source resistances for the nmos and pmos transistor respectively.

BW of the Inverter trans-impedance amplifier is

$$BW = \frac{A_{inv} + 1}{2 \pi (R_0 + R_F) C_{im}}$$

(11)

Fig-4: Inverter TIA (Inv-TIA)

Retrieval Number:100.1/ijvlsid.C1206031322 DOI:10.54105/ijvlsid.C1206.031322 Journal Website: www.ijvlsi.latticescipub.com

Published By: Lattice Science Publication (LSP) © Copyright: All rights reserved.

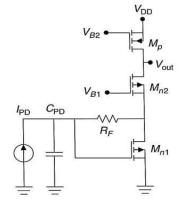

#### E. Current Reuse TIA (CR-TIA)

Topology are configured using CS-TIA(M<sub>n1</sub>) with shunt feedback resistor ( $R_F$ ) cascade with CG-TIA( $M_{n2}$ ) shown on figure.5 [26]. The The amplified output of first stage CS-TIA is applied to CG-TIA to further increase Transimpedance gain which is taken out from Vout . Along with high gain, bandwidth is also increased because of reduced miller capacitance. current reuse provide higher GBW product. Open loop gain (A1) for CS stage of current reuse TIA is

$$A_1 = -g_{mn1}R_{CS} \tag{12}$$

Here Rcs is the parallel combination of R<sub>DS1</sub>, R<sub>DS2</sub> and inverse of gmn2

Open loop gain (A<sub>2</sub>) for CG stage (A2) of current reuse TIA is

$$A_2 = g_{mn2} \left(\frac{R_{DSP}R_{DSN2}}{R_{DSP} + R_{DSN2}}\right) \tag{13}$$

Bandwidth of current reuse-TIA is given by

$$\frac{A_1 + 1}{2\pi f C_{pd}(R_{CS} + R_F)} \tag{14}$$

Where  $R_{cs}$  - total drain resistance of  $M_{n1}$ ,  $A_1$  and  $A_2$ .

Fig-5: Current Reuse-TIA (CR-TIA)

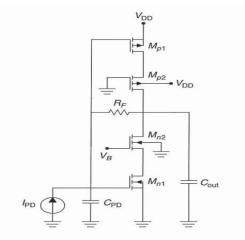

#### F. Inverter-Cascode (InvCas-TIA)

Configuration is shown in figure.6 [26]. Here NMOS  $(M_{n2})$ and PMOS (M<sub>p2)</sub> transistor are connected in series with M<sub>p1</sub> and M<sub>n1</sub> inverter transistor. In InvCas-TIA voltage gain is higher than Inv-TIA because of high output resistance of InvCas-TIA, also transimpedance gain is somewhat also higher because of high voltage gain. For two reason the bandwidth of InvCas-TIA is higher, First miller effect and second high voltage gain InvCas Transimpedance amplifier. Gain and Bandwidth can be calculated by:

OL Gain (A<sub>InvCas</sub>) of Inverter Cascode Transimpedance Amplifier is shown as-

$$A_{InvCas} = -g_m R_o \tag{15}$$

And, Bandwidth of Inverter cascode is

$$BW = \frac{R+1}{2\pi (R_0 + R_F)C_{pd}} \tag{16}$$

Retrieval Number: 100.1/ijvlsid. C1206031322 DOI:10.54105/ijvlsid.C1206.031322 Journal Website: www.ijvlsi.latticescipub.com

Fig-6: Inverter Cascode-TIA

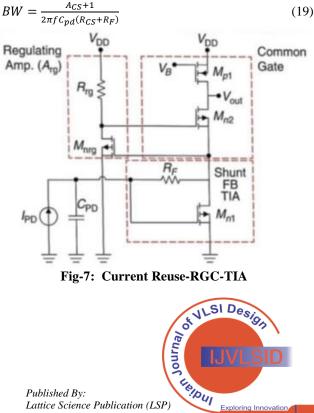

#### G. Current-reuse (CR) RGC TIA

CR RGC TIA configuration ,a regulated cascode TIA (RGC-TIA) are widely used reason being it's low input impedance but for further reducing the low input impedance current reuse technique is used in RGC-TIA shown in figure.7.[26] This CR-RGC-TIA increases the transconductance by  $2g_m = (g_{mp} + g_{mn})$  that is double of RGC TIA [31] Its gain and bandwidth are shown below :

OL Gain of common source (CS) amplifier (Acs) and of RGC (A<sub>RGC</sub>) amplifier are:

$$A_{CS} = -g_{mn1}R_{CS} \tag{17}$$

Where Rcs is the parallel combination of R<sub>ON1</sub>, RON2 and inverse of gmn2

$$A_{RGC} = g_{mn2} \frac{(R_{DSP1}R_{DSN2})}{(R_{DSP1} + R_{DSN2})}$$

(18)

Bandwidth (BW) of current reuse regulated cascode TIA is as-

ww.iivlsi.latticescipub

© Copyright: All rights reserved.

12

# A Comparative Analysis of Gain and Bandwidth of CMOS Transimpedance Amplifier

Above shown topologies of trans-impedance amplifier shows the pros and cons on the basis of parameter like gain and bandwidth.

#### III. **RECENT ADVANCEMENTS**

In this section we have discussed some of the latest research work has been shown in this area which is based on increasing the bandwidth (BW) and gain. The effect of parasitic of photodiode capacitance make's it arduous to get large bandwidth in TIA. The TIA presented in [37] uses shunt-shunt feedback topology to enhance the Transimpedance amplifier BW. For enhancing the Bandwidth of TIA, Dynamic threshold MOS transistor (DTMOS) can also be used [9].In [32] using DTMOS method to increase the trans-conductance of the MOS which in turn increases the bandwidth using the composite transistor structure. The gain of TIA can also be increased using floating gate metal oxide semiconductor (FGMOS) in [10]. The Bandwidth and phase margin (PM) can be significantly increased in [17] by replacing feedback resistor with Tee network circuit. The TIA presented in [33] uses a floating-active inductor (FAI) which is based on gyrator-C structure with a combination of capacitive degeneration, broadband Matching Network, and Regulated cascode to enhance bandwidth and Gain.

So, There is several ways to attain desired result in terms of it's gain and bandwidth (BW) by analyzing and studying the resent work in this field.

#### IV. **FUTURE SCOPE**

Design of TIA need to be optimized carefully for the Trade-offs such as BW, gain, noise, as well as power consumption. For low voltage applications, Low voltage circuit techniques such as Floating gate MOS (FGMOS), Quasi floating gate MOS (QFGMOS), bulk driven technique, Dynamic Threshold MOS etc can be used as well as for minimizing the power consumption these technique can be useful. Various Bandwidth extension techniques such as shunt peaking and Capacitive Degeneration along with many circuit techniques can be applied in a TIA to improve performance. Also for improving the bandwidth demands in TIA cascading can be done of different stages that will enhance the gain and also improves the parasitic capacitance effect.

| Table-I. | Performance | Comparison | of Various | <b>Topologies of TIA</b> |

|----------|-------------|------------|------------|--------------------------|

|----------|-------------|------------|------------|--------------------------|

| Ref.<br>No | Year | Technology<br>(CMOS) | TIA Gain<br>(dBΩ) | Bandwidth<br>(GHz) | Power/Supply<br>(Volts) | Topology/Technique                                                                                        |

|------------|------|----------------------|-------------------|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| [20]       | 2004 | 0.6 µm               | 54                | 9.2                | 2.5 V                   | Interstage matching network technique                                                                     |

| [8]        | 2006 | 0.18 µm              | 52                | 7.6                | 2 V                     | Regulated cascode                                                                                         |

| [24]       | 2007 | 0.18 µm              | 53                | 8                  | 1.8 V                   | Regulated cascode                                                                                         |

| [30]       | 2010 | 0.18 µm              | 54.6              | 7                  | 1.8 V                   | Common gate with active feedback                                                                          |

| [28]       | 2011 | 0.18 µm              | 40                | 8.69               | 1.8 V                   | RGC- Resistive feedback, source follower and capacitive degeneration.                                     |

| [19]       | 2013 | 0.40 µm              | 47                | 8                  | 1.1 V                   | Inverter, active CD feedback (ICDF-TIA)                                                                   |

| [17]       | 2014 | 0.65 µm              | 52                | 50                 | 1.2 V                   | Differential, peaking technique, RGC input stage with a shunt-feedback.                                   |

| [34]       | 2015 | 0.18µm               | 50                | 7                  | 1.5V                    | Regulated Cascode (RGC)                                                                                   |

| [5]        | 2015 | 0.18µm               | 61                | 15                 | 3.3 V                   | Regulated Cascode                                                                                         |

| [15]       | 2015 | 0.13 µm              | 61.6              | 2                  | 1.5 V                   | Current Reuse, inductor peaking technique                                                                 |

| [12]       | 2016 | 0.18µm               | 1.8kΩ             | 7.2                | -                       | Regulated Cascode, multilevel active feedback<br>(MLAF) structure, inductorless CMOS<br>differential TIA. |

| [7]        | 2017 | 0.18µm               | 59                | 7.9                | 1.8 V                   | active voltage-current feedback,                                                                          |

| [10]       | 2017 | 0.18µm               | 37.7              | 13.5               | 1 V                     | FGMOS, active feedback and shunt peaking network.                                                         |

| [4]        | 2018 | 0.90 µm              | 40.5              | 7                  | 1 V                     | active inductive peaking at output load                                                                   |

| [2]        | 2018 | 0.65 µm              | 62                | 11                 | -                       | regulated cascode (RGC), current reuse strategy                                                           |

| [21]       | 2018 | 0.18 µm              | 56.8              | 5                  | 1 V                     | FGMOS,Wilson current mirror                                                                               |

| [3]        | 2019 | 0.18 µm              | 49.7              | 9.2                | 1.8V                    | RGC Structure with MOS-based Immittance<br>Converter (MIC)                                                |

| [13]       | 2020 | 0.90 µm              | 40.6              | 3.7                | 1.2V                    | RGC , level shifter and a common source structure                                                         |

#### V. CONCLUSION

Apart from topology device technology, considering the bandwidth and gain, different TIA topologies. has been studied and presented. FGMOS provides best result in terms of High gain, low power supply, Bandwidth and power dissipation. Common Gate TIA and Regulated Cascode TIA provide best results in terms of Higher

Bandwidth and minimum power consumption. Likewise in terms of Current Reuse RGC gives high transimpedance across a large bandwidth. Similarly in terms of low power consumption,

Retrieval Number: 100.1/ijvlsid. C1206031322 DOI:10.54105/ijvlsid.C1206.031322 Journal Website: www.ijvlsi.latticescipub.com

Published By:

Higher gain and High gain-Bandwidth product Inverter Cascode TIA and Regulated cascode TIA seems to be a good choice. To achieve the best characteristics by introducing various bandwidth extension technique, these topologies can be further improved.

### REFERENCES

- ima Honarmand *et al.*, Design of an Inverter-Base, activefeedback,Low-Power Transimpedance Amplifier Operating at 10Gbps, *Journal of Circuits, Systems and Computers*, December 2019. [CrossRef]

- Robert Costanzo, Student Member, IEEE, and Steven M. Bowers, Member, IEEE, "A Current Reuse Regulated Cascode CMOS Transimpedance Amplifier With11-GHz Bandwidth", IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, VOL. 28, NO. 9, pp. 816 – 818,SEPTEMBER 2018. [CrossRef]

- Maryam Hosseini, Roya Jafarnejad, Jafar Sobhi, Ziaaddin Daie Koozehkanani, A low power wideband RGC-based modified-MIC trans-impedance amplifier in 0.18µm CMOS process, Microelectronics Journal (2019). [CrossRef]

- Soorena Zohoori , Mehdi Dolatshahi , Majid Pourahmadi , Mahmoud Hajisafari , "A CMOS, low-power current-mirror-based transimpedance amplifier for 10 Gbps optical communications", Microelectronics Journal 80, pp. 18-27,2018 [CrossRef]

- Qiwei Song, Luhong Mao "Wideband sige BICMOS transimpedance amplifier foe 20 Gb/s optical links", *IEICE electronics express*, Vol. 12, No. 13, july 2015, pp. 1-8, 2015. [CrossRef]

- Priya Singh, Vandana Niranjan, Ashwni Kumar, "45nm CMOS Low Power Multilevel Active Feedback Transimpedance amplifier for Optical Receivers" Circuit World 2021 [CrossRef]

- Mahmood Seifouri, Parviz Amiri, Iman Dadras, "A transimpedance amplifier for optical communication network based on active voltagecurrent feedback", *Microelectronics Journal* 67 (2017) 25–31,2017 [CrossRef]

- Huei-Yan Hwang, Jun-Chau Chien , "A CMOS Tunable Transimpedance Amplifier" , *IEEE Microwave And Wireless Components Letters*, Vol. 16, No. 12, December 2006 [CrossRef]

- Priya Singh, Vandana Niranjan, Ashwni Kumar, "10.56 GHz Transimpedance Amplifier (TIA) Using Dynamic Body Bias Technique with Low Power Dissipation of 0..438mW'' International Journal of Electronics Engineering, Vol.11, No.2, pp. 416-425, June-Dec 2019

- Urvashi Bansal, Maneesha Gupta. "High bandwidth transimpedance amplifier using FGMOS for low voltage operation", *INTEGRATION* the VLSI journal (2017). [CrossRef]

- 11. Priya Singh, Vandana Niranjan, Ashwni Kumar "Low Noise And Low Power Transimpedance Amplifier using Inverter Based Local Feedback" International Conference on Smart Generation Computing, Communication and Networking (SMARTGEN), AISSMS College of Engineering ,Pune, Oct 29-30, 2021 [CrossRef]

- Oscal T.-C. Chen, Cheng-Ta Chan, and Robin R.-B. Sheen, "Transimpedance Limit Exploration and Inductor-Less Bandwidth Extension for Designing Wideband Amplifiers", IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 24, NO. 1, pp. 348-352, JANUARY 2016 [CrossRef]

- Reza Saffari, Mehdi Dolatshahi, Soorena Zohoori, "A Fullyintegrated, Low-Power Transimpedance Amplifier for 5Gbps Optical Front-End", 2020 28th Iranian Conference on Electrical Engineering (ICEE),2020. [CrossRef]

- Nidhi Singh, Vandana Niranjan, "Wide Band Transimpedance Amplifier using Class AB FVF" IEEE International Conference on Recent Developments in Control, Automation & Power Engineering (RDCAPE-2019), Amity University Uttar Pradesh, Noida, UP, October 10-11, 2019 [CrossRef]

- 15. Ehsan Semsar Parapari, Elmira Semsar Parapari, Ziaaddin Daei Koozehkanani, "A Broadband Transimpedance Amplifier (TIA) for Visible Light Communication in 0.18 µm CMOS", 2020 28th Iranian Conference on Electrical Engineering (ICEE). [CrossRef]

- Diaa Abd-elrahman,Mohamed Atef I, Mohamed Abbas and Mohamed Abdelgawad, "Current-Reuse Transimpedance Amplifier withActive Inductor", 2015 International Symposium on Signals, Circuits and Systems (ISSCS), July 2015 [CrossRef]

- Rui Yang, Shao-Wei Zhen, You-Run Zhang, Yi-Qiang Zhao, Xiao Yang, Bo Zhang, "A wideband transimpedance amplifier with tee network topology", 2020 IEEE 15<sup>th</sup> International Conference on Solid-

State & amp; Integrated Circuit Technology (ICSICT),2020. [CrossRef]

- Sang Gyun Kim, Seung Hwan Jung, Yun Seong Eo, Seung Hoon Kim, Xiao Ying, Hanbyul Choi, Chaerin Hong, Kyungmin Lee, and Sung Min Park, "A 50-Gb/s Differential Transimpedance Amplifier in 65nm CMOS Technology", 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2014.

- Anatoly V. Kosykh, Sergey A. Zavyalov, Rodion R. Fakhrutdinov, Konstantin V. Murasov, Ruslan A. Wolf, "Differential Broadband Transimpedance Amplifier in 130 nm SiGe BiCMOS", 19<sup>th</sup> INTERNATIONAL CONFERENCE ON MICRO/NANOTECHNOLOGIES AND ELECTRON DEVICES EDM 2018. [CrossRef]

- Mohamed Atef & Horst Zimmermann, "Low-power 10 Gb/s inductorless inverter based common-drain active feedback transimpedance amplifier in 40 nm CMOS", *Analog Integrated Circuits and Signal Processing* volume 76 pp. 367–376, 2013 [CrossRef]

- Preeti Singh, Maneesha Gupta. "Application of FGMOS Based Wilson Current Mirror in Transimpedance Amplifier", 2018 8th IEEE India International Conference on Power Electronics (IICPE), 2018. [CrossRef]

- Behnam Analui, and Ali Hajimiri, "Bandwidth Enhancement for Transimpedance Amplifiers", *IEEE Journal Of Solid-State Circuits*, Vol. 39, No. 8, August 2004 [CrossRef]

- Cheng Li, StudentMember, IEEE, and Samuel Palermo, Member, IEEE, "A Low-Power 26-GHz Transformer-Based Regulated Cascode SiGe BiCMOS Transimpedance Amplifier", 1264 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 5, pp. 1264 – 1275,MAY 2013 [CrossRef]

- 24. Davender Singh, Ajay Shankar & Manoj Kumar, "A Study on Transimpedance Amplifier in 0.35 µm CMOS Technology", International Journal of Computer Applications (0975 – 8887) Volume 51-No.21, August 2012 [CrossRef]

- 25. Chih-Kang Chien, Hsieh-Hung Hsieh, Member, IEEE, Huan-Sheng Chen, and Liang-Hung Lu, Member, IEEE, "A Transimpedance Amplifier With a Tunable Bandwidth in 0.18-μm CMOS", IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 58, NO. 3, pp. 498-505, MARCH 2010. [CrossRef]

- Dr. Suresh Kumar & Vanita, "A Review of Transimpedance Amplifiers Used in Biomedical Applications", 2021 5th International Conference on Computing Methodologies and Communication (ICCMC), 2012. [CrossRef]

- 27. Dandan Chen, Kiat Seng Yeo, Senior Member, IEEE, Xiaomeng Shi, Manh Anh Do, Senior Member, IEEE, Chirn Chye Boon Senior Member, IEEE, and Wei Meng Lim, "Cross-Coupled Current Conveyor Based CMOS Transimpedance Amplifier for Broadband Data Transmission", IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 8, pp. AUGUST 2013. [CrossRef]

- Taiyi Huang, Qihui Zhang, Weifeng Zhang, "A Novel Transimpedance Amplifier for 10 Gbit/s Optical Communication System", 2011 9th IEEE International Conference on ASIC, 2011. [CrossRef]

- Omeed Momeni, Student Member, IEEE, Hossein Hashemi, Member, IEEE, and Ehsan Afshari, Member, IEEE, "A 10-Gb/s Inductorless Transimpedance Amplifier", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS, VOL. 57, NO. 12, pp. 926-930 DECEMBER 2010 [CrossRef]

- Z. Lu, K. S. Yeo, W. M. Lim and M. A. Do, "Design of a CMOS Broadband Transimpedance Amplifier With Active Feedback", *IEEE Transactions on VLSI Systems*, vol. 18, no. 3, pp.- 1964 – 1972, March 2010. [CrossRef]

- 31. Akira Hida, Yusuke Nakane, Shunta Mizuno, Makoto Nakamura,Daisuke Ito, Shinsuke Nakano, and Hideyuki Nosaka, "A wideband current-reuse-RGC TIA circuit with low-power consumption, IEICE Electronics Express, Vol.16, No.22, 1–4,2019. [CrossRef]

- 32. Jawdat Abu-Taha, "High Gain, Widebandwidth and Low PowerTransimpedance Amplifier Using DTMOS Transistor", 2019 IEEE 7th Palestinian International Conference on Electrical and Computer Engineering (PICECE),March 2019 [CrossRef]

Retrieval Number:100.1/ijvlsid.C1206031322 DOI:<u>10.54105/ijvlsid.C1206.031322</u> Journal Website: <u>www.ijvlsi.latticescipub.com</u>

Published By: Lattice Science Publication (LSP) © Copyright: All rights reserved.

- Xiangyu Chen and Yasuhiro Takahashi, "Design of a CMOS Broadband Transimpedance Amplifier with Floating Active Inductor", 2019 IEEE Computer Society Annual Symposium on VLSI (ISVLSI),july 2019. [CrossRef]

- Mahmood Seifouri , ParvizAmiri,MajidRakide," "Design of broadband transimpedance amplifier for optical communication systems", Microelectronics Journal 46 (2015) pp.679–684680, 2015. [CrossRef]

- 35. Nidhi Singh, Vandana Niranjan, "Wide Band Transimpedance Amplifier using Class AB FVF" IEEE International Conference on Recent Developments in Control, Automation & Power Engineering (RDCAPE-2019), Amity University Uttar Pradesh, Noida, UP, October 10-11, 2019. [CrossRef]

- Mishra and Vandana Niranjan, "Gain And Bandwidth Boosting Of Transimpedance Amplifier", IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology (RTEICT), Bangalore, India, 18- 19 May 2018. [CrossRef]

- 37. Abu-Taha, J.Y. and M. Yazgi, Improving the bandwidth of the transimpedance amplifier based on CS stages in cascade configuration using impedance matching techniques. Analog Integrated Circuits and Signal Processing, 2016.89(3): p. 685-691. [CrossRef]

### **AUTHOR PROFILE**

Vineeta Singh, received bachelor's degree (Hons.) in Electronics from Shaheed Rajguru college of Applied Science For Women (Delhi university), New Delhi, India and M.Sc degree in Electronics from Kurukshetra University, Haryana, India. She is currently pursuing the M.Tech degree in VLSI Design from Indira Gandhi Delhi Technical University For Women (IGDTUW),

New Delhi, India. Areas of Interest are Low voltage CMOS Circuits, VLSI Circuits and Analog Circuits.

Sarika Parihar, received bachelor's degree in Computer science from Jai narain college of technology and science, Bhopal, India. She is currently pursuing the M.Tech degree in VLSI Design from Indira Gandhi Delhi Technical University For Women (IGDTUW), New Delhi, India. Areas of Interest are Low voltage Analog design, CMOS Circuits, VLSI Circuits and

Analog Circuits.

**Prof. Vandana Niranjan** is working as Professor in the Department of Electronics and Communication Engineering at Indira Gandhi Delhi Technical University Delhi, India. She graduated in the year 2000 and received her B.E. degree in Electronics and Communication Engineering from Government Engineering College Institute of Technology of Raiiy Gandhi Proudvogić

(now University Institute of Technology of Rajiv Gandhi Proudyogiki Vishwavidyalaya) Bhopal. In the year 2002, she received her M.Tech degree from the Department of Electronics and Communication Engineering at Indian Institute of Technology (IIT) Roorkee with VLSI Design as specialization. In the year 2015, she was awarded her Ph.D degree in the area of Low Voltage VLSI Design from University School of Engineering & Technology, GGSIP University Delhi. She has a teaching and research experience of approximately 20 years at Indira Gandhi Delhi Technical University Delhi. Her areas of interest includes MOSFET body bias techniques and Low-voltage Low-Power Analog CMOS circuit design. She has several publications to her credit in various international journals and conferences and Book chapters.

Retrieval Number:100.1/ijvlsid.C1206031322 DOI:10.54105/ijvlsid.C1206.031322 Journal Website: www.ijvlsi.latticescipub.com